This electronic document has been provided by the Kent State University Interlibrary Loan Department. This material may be protected by United States Copyright Law (Title 17, U.S. Code).

| <b>ILLiad</b> | TN: | 224462 |

|---------------|-----|--------|

|               |     |        |

**Borrower: KSU**

Lending String: \*WSU,OSU,SEA,TKN,KKU

Patron: Yuan, Man

**Journal Title:** Proceedings of the 1975 Sagamore Computer Conference on Parallel Processing; papers presented on August 19-22, 1975.

Volume: Issue:

Month/Year: 1975Pages: 167-eoa

**Article Author:**

Article Title: K.E. Batcher; The Multi-Dimensional

Access Memory in STARAN

Wednesday, March 28, 2012

Call #: 82467110401

Location:

Charge

Maxcost: \$50IFM

**Shipping Address:**

Library-Interlibrary Loan (OHIOLINK)

Kent State University (208)

P.O. Box 5190 One Eastway Drive Kent, OH 44242-0001

Fax:

Ariel: 131.123.20.192

Email: Ims-ill@kent.edu

Imprint: Silver Spring, Md.; IEEE Computer Socie

ILL Number: 89127594

NOTICE: THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE)

Sent By:

DUNBAR LIBRARY – INTERLIBRARY LOAN WRIGHT STATE UNIVERSITY DAYTON, OH 45435-0001 PHONE: (937)775-4110

FAX: (937)775-2356 EMAIL: dill@www.libraries.wright.edu

If there are problems with this ARIEL document:

| - | Missing Pages: Page #s  |  |

|---|-------------------------|--|

| - | Edges cut off: Page #s  |  |

| - | Unable to read: Page #s |  |

| _ | Other:                  |  |

Please return this page to us via ARIEL or FAX, or you may call us and we will fix the problem.

THANK YOU FOR SELECTING THE DUNBAR LIBRARY – INTERLIBRARY LOAN DEPARTMENT

by sigerson.sword.org (8.14.3/8.14.3/Debian-5) with ESMTP id q2SDiTgi0191 by mualmarp01.mcs.muohio.edu (8.13.8/8.13.8) with ESMTP id q2SDjh

£4027900

26

Content-transfer-encoding: 7BIT

(Sun Java(tm) System Messaging Server 6.3-8.01 (built Dec 16 2008; 64bit))

id <0M1L00G00KW4RS00@sms3.wright.edu> for requests@sword.org; Wed,

28 Mar 2012 09:45:43 -0400 (EDT)

by sms3.wright.edu

(Sun Java(tm) System Messaging Server 6.3-8.01 (built Dec 16 2008; 64bit)) with ESMTP id <0M1L00GB0KW72U10@sms3.wright.edu> for requests@sword.org; Wed,

28 Mar 2012 09:45:43 -0400 (EDT)

Date: Wed, 28 Mar 2012 09:45:44 -0400

From: Dunbar Interlibrary Loan <dill@www.libraries.wright.edu>

Subject: Please fill request

To: requests@sword.org

X-Virus-Scanned: by bsmtpd at muohio.edu

Rule breakdown below

pts rule name

description

THIS MATERIAL MAY RE PROTECTED BY CONTRICET LAW (TITLE 17, U.S. COOK

\*\*\* Generated by ILLiad

Request sent by PAUL LAURENCE DUNBAR LIBRARY WRIGHT STATE UNIVERSITY

Call Number/BARCODE NUMBER: 82467110401

DD scauned 3-28-12

Journal Title: Proceedings of the 1975 Sagamore Computer Conference on Parallel P rocessing ; papers presented on August 19-22, 1975.

Article Author:

Article Title: K.E. Batcher; The Multi-Dimensional Access Memory in STARAN

Journal Vol: Journal Issue:

Journal Month: Journal Year: 1975

Article Pages: 167-eoa

Notes:

Branch Location:

Borrower: KSU

Patron: Yuan, Man

Mail

Library- Interlibrary Loan (OHIOLINK)

Kent State University (208)

P.O. Box 5190

One Eastway Drive

Fax:

Ariel: Yes 131.123.20.192

This request has been forwarded from ILL by steve - Lending. Illiad Transaction Number: 224462

89127594 Part 1

## Summary\*

## THE MULTI-DIMENSIONAL ACCESS MEMORY IN STARAN

By Kenneth E. Batcher

Digital Technology Department Goodyear Aerospace Corporation Akron, Ohio

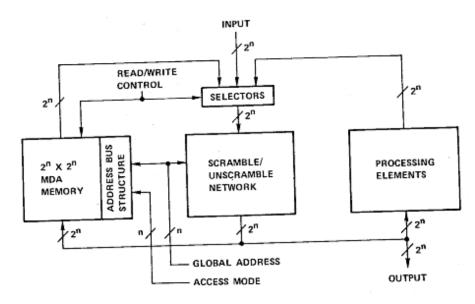

Each array module in the STARAN<sup>†</sup> associative array processor contains a 256 × 256 multidimensional access (MDA) memory (see illustration). Parallel vector arithmetic and associative search operations access memory data by bit-slices, while input, output, and scalar arithmetic operations access memory data by words. The MDA memories use standard random-access memory (RAM), integrated-circuit chips in a novel configuration. Use of standard, high-volume, low pin-count memory devices in place of custom LSI devices reduces costs significantly.

To achieve multidimensional access, data are stored in a scrambled pattern; bit B of word W is stored in bit-location B of memory chip B  $\oplus$  W where  $\oplus$  indicates a component-by-component exclusive-or.

Data are accessed by specifying a stencil shape with an 8-bit access mode and a stencil position with an 8-bit global address. The 256 memory bits covered by a stencil can be fetched or stored in one memory cycle.

The address bus structure of the MDA memory has 16 address lines (as opposed to 8 lines for a conventional RAM). For  $k=1,\,2,\,\ldots,\,8$  address line  $x_k$  is fed by the  $k^{th}$  bit of the global address,

while address line  $y_k$  is fed by the exclusive-or of the  $k^{th}$  bits of the access mode and the global address. Address pin k of memory chip  $\{c_1c_2, \ldots c_8\}$  is connected either to  $x_k$  if  $c_k = 0$  or to  $y_k$  if  $c_k = 1$ .

Memory data are scrambled and unscrambled by a scramble/unscramble network, which can also shift and perform other useful permutations on data fetched from memory.

When memory data are fetched or stored with access mode M and global address G, processing element P accesses bit  $(\overline{M}\cdot G) \oplus (M\cdot P)$  of memory word  $(M\cdot G) \oplus (\overline{M}\cdot P)$ , where logical negation is indicated by "-" and the logical product ("and") is indicated by ".".

Bit-slice access is obtained with M = (000000000)and word access is obtained with M = (111111111). Other access modes allow data to be accessed in other ways.

<sup>&</sup>lt;sup>†</sup>TM, Goodyear Aerospace Corporation, Akron, Ohio

Block Diagram of STARAN Array Module

<sup>\*</sup>This is a summary of a paper that has been submitted for publication in the IEEETC Special Issue on Parallel Processing