# **Sequential Circuits**

- For several lectures, we have studied combinational circuits — circuits whose output values depend <u>only</u> on the inputs

- Now we will study sequential circuits circuits whose output values depend on <u>both</u>:

- the inputs, and

- the current state of the circuit

- The state of the circuit is defined by the values stored in the memory elements

- With sequential circuits, we can build registers, memories, shift registers, counters, stacks, queues, etc.

- With combinational circuits, we can build adders, ALUs, and glue logic

Fall 1998, Lecture 08

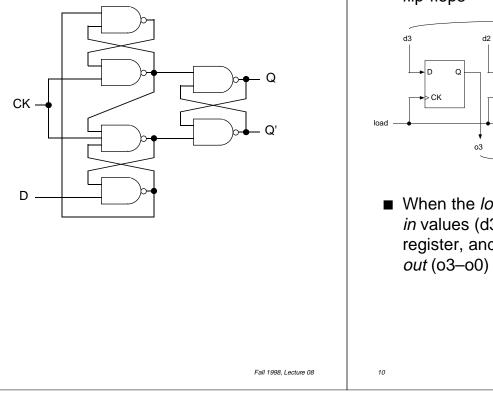

## The D Latch (Gated D Flip-Flop)

- Inputs:

- D = data

- CK = clock

- Outputs:

- Q

- Q'

- Operation:

- When CK is 1, Q follows D (if D changes, Q changes also, after a short delay)

D

CK

Q

Q'

- Otherwise, Q keeps its last value

- Note that the D latch keeps its value while CK is 0 (it's a sequential circuit)

- It's a memory!!

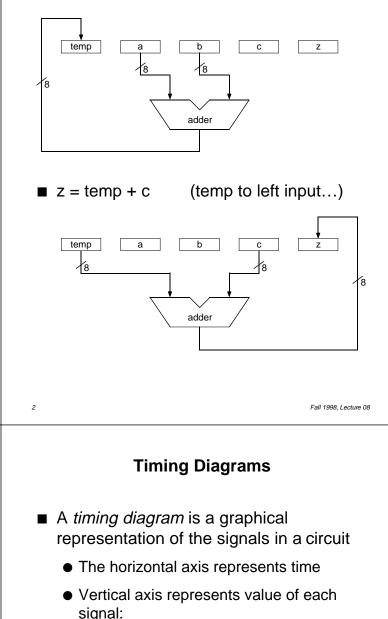

■ temp = a + b

(a to left input...)

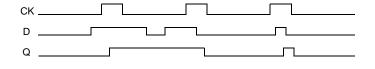

- A 1 is represented as a high line

- A 0 is represented as a low line

- The timing diagram may account for propagation delay — the delay through a combinational element (the amount of time it takes to execute)

- Timing diagram illustrating the operation of a D latch:

Fall 1998, Lecture 08

## Clock

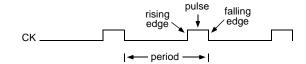

It is common for a digital system to have a *clock* signal, which repeats a 0-1 pattern at regular intervals

- The *period* is the length of time that it takes to repeat the pattern

- The part of the pattern which has the value of 1 is called the clock *pulse*

- The 0-1 transition is called the *rising* (or *positive*) *edge*

- The 1-0 transition is called the *falling* (or *trailing*, or *negative*) *edge*

- Clock signals are used in synchronous circuits — those where events happen at predictable, regular intervals

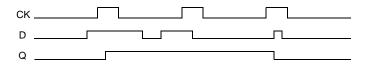

#### The (Edge-Triggered) D Flip-Flop

D

CK

Q

Q'

Inputs:

5

- D = data

- CK = clock

- Outputs:

- Q

- Q'

- Operation:

- When CK transitions from 0 to 1 (leading edge), Q is set to the value of D (after a short delay)

- Otherwise, Q keeps its last value, regardless of any changes in D

- We can use n D flip-flops to build an n-bit register...

#### Can We Use a D Latch as a Register?

- Potential problem: output is unstable anytime CK is 1

- Can't use as register, since register is in a closed feedback loop — can't allow values to change while they're being used in a computation

- Want to change register values only when computation is complete

- Read values and compute (generating garbage output until finished)

- At end of cycle, when result is ready, store into register

- Must make cycle long enough to allow result to stabilize!

- Useful for holding values to transfer outside the circuit

- OK here since we'll produce a result, and then tell outside when it's safe to read it

D Latch vs. D Flip-Flop

- Not useful in building registers

- D Flip-Flop:

- When CK transitions from 0 to 1 (leading edge), Q is set to the value of D (after a short delay)

• Useful as a memory element in a register

8

Fall 1998, Lecture 08

6

Fall 1998, Lecture 08

# **Building a D Flip-Flop**

Implementation is fairly complicated to analyze...

9

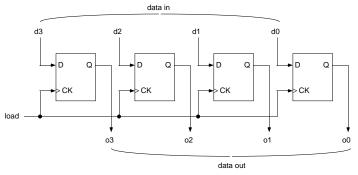

# **Building a Register Out of D FFs**

This simplified diagram shows how a 4bit register can be constructed out of 4 D flip-flops

When the *load* signal goes high, the *data in* values (d3–d0) are stored in the register, and become available as *data out* (o3–o0) signals

Fall 1998, Lecture 08