## **Chapter 9's Simple Machine**

- Uses 16-bit word

- 16 general-purpose registers named R0 through R15

- R0 is hardwired to contain the value 0

#### 4 types of instructions

- Data migration (load, store, ...)

- Data manipulation (add, sub, ...)

- Loading immediate values into registers

- Unconditional and conditional branching

- 3 machine language instruction formats

- 3-register format used by data transfer and data manipulation instructions

- Immediate format

- Branching format

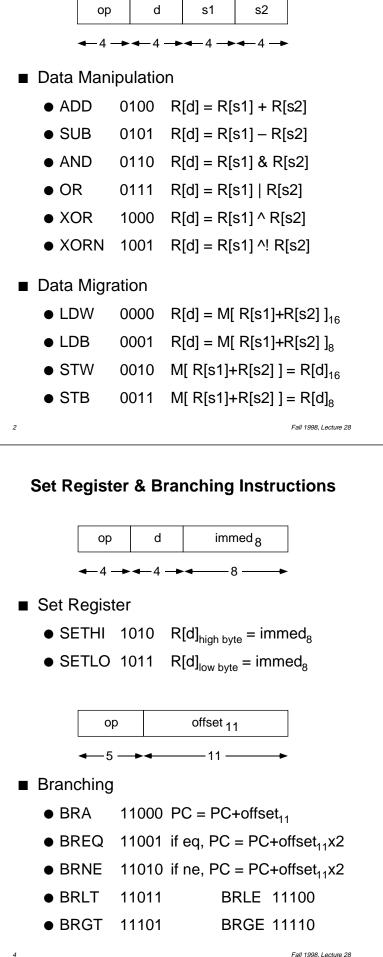

### **Data Migration & Manipulation** Instructions (cont.)

- The format for these instructions uses

- 4 bits to specify the opcode

- 4 bits to specify each register

- Data manipulation instructions

- Each line here lists:

- assembler mnemonic,

- the opcode, and

- pseudocode specifying the operation

- Op dest, s1, s2

3

- Same order as text so far, backwards from SPARC assembler on nimitz

- Data migration (load & store) instructions

- Think of R[s1] as the base register, and R[s2] as the displacement

- Word version and byte version of each

- LDB does sign extension, STB stores least significant byte

Fall 1998. Lecture 28

Fall 1998, Lecture 28

### **Data Migration & Manipulation** Instructions

# Set Register & Branching Instructions (cont.)

- "set register" instructions

- 4 bits for opcode, 4 bits to specify register

- 8 bits for immediate value

- Set the high or low byte of the register with the immediate value

- The other byte is not affected

- Unconditional and conditional branch instructions

- BRA (branch always = unconditional jump)

- BREQ, etc. (conditional branch)

- These instructions specify an offset, rather than an absolute address

- This is the PC-relative addressing mode

- Note that 2x that offset is used since branch will always go to a word boundary

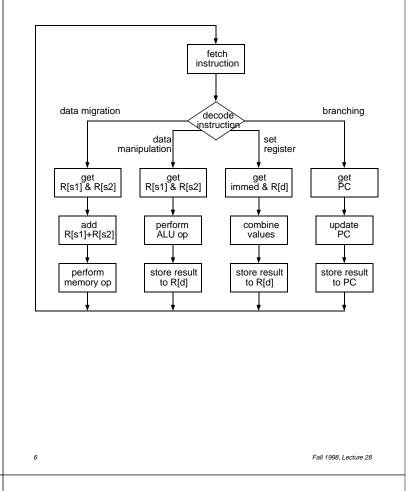

# Instruction Decode / Execute Loop

## Instruction Decode / Execute Loop (cont.)

Fetch instruction

5

- Get the next instruction from memory, store it in the Instruction Register (IR), and increment the PC

- Decode instruction

- Decode the opcode field of the IR to determine what kind of instruction is being executed

- Execute instruction

- Data manipulation

- Use ALU to perform operation

- Data migration

- Combine R[s1] and R[s2] using ALU

- Load from or store to memory

- Set register

- Combine immed with specified byte of R[d]

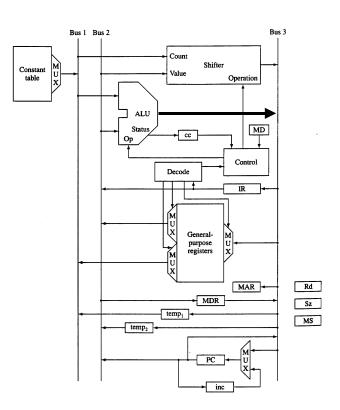

## Implementation of Simple Machine

Diagram from Computer Systems, Maccabe, Irwin 1993

8

Fall 1998, Lecture 28