Fall 2003, Lecture 27

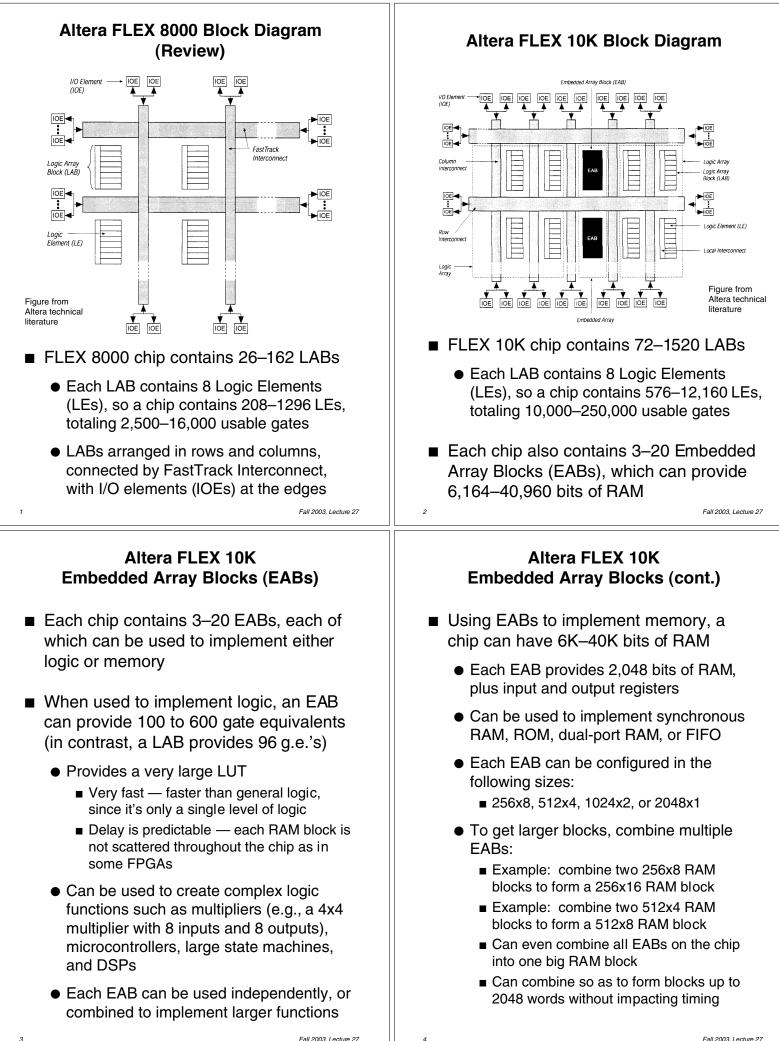

## Altera FLEX 10K Altera APEX 20K Overview Embedded Array Blocks (cont.) APEX 20K chip contains: ₹t • 256–3.456 LABs. each of which contains 10 Logic Elements (LEs), so a chip contains 2,560-51,840 Les, 162,000-2,391,552 usable gates 16–216 Embedded System Blocks (EABs), each of which can provide 32,768-442,368 bits of memory 256 × 8 512 × 4 1,024 × 2 Can implement CAM, RAM, dual-port RAM, Column -----Interconnect ROM, and FIFO Organization: MultiCore architecture, combining LUT, product-terms, & memory in one structure Designed for "system on a chip" Figure from Altera technical literature MegaLAB structures, each of which EAB gets input from a row channel, and contains 16 LABs, one ESB, and a can output to up to 2 row channels and 2 MegaLAB interconnect (for routing within column channels the MegaLAB) ESB provides product terms or memory Input and output buffers are available Fall 2003. Lecture 27 Fall 2003. Lecture 27 5 **APEX Embedded System Blocks** APEX LABs and Interconnect (ESBs) Logic Array Block (LAB) Each ESB can act as a macrocell and provide product terms • 10 LEs Each ESB gets 32 inputs from local Interleaved local interconnect (each LE) connects to 2 local interconnect, each interconnect, from adjacent LAB or local interconnect connects to 10 LEs) MegaLAB interconnect Each LE can connect to 29 other Les In this mode, each ESB contains 16 through local interconnect macrocells, and each macrocell contains 2 product terms and a programmable ■ Logic Element (LE) register (parallel expanders also provided) • 4-input LUT, carry chain, cascade chain, same as FLEX devices ■ Each ESB can also act as a memory • Synchronous and asynchronous load and block (dual-port RAM, ROM, FIFO, or clear logic CAM memory) configured in various sizes Inputs from adjacent local interconnect, Interconnect which can be driven from MegaLAB or MegaLAB interconnect between 16 LABs, FastTrack interconnect etc. inside each MegaLAB Outputs to MegaLAB and FastTrack, some • FastTrack row and column interconnect outputs to local interconnect between MegaLABs

7

Fall 2003, Lecture 27