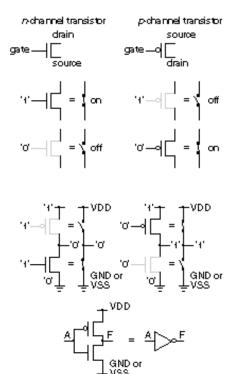

#### **CMOS Transistor Notation**

- A CMOS transistor has 3 terminals, called the gate, source, and drain

- V<sub>AB</sub> is the voltage between nodes A and B in a circuit

- Positive power supply (power source)

- In TTL, written V<sub>CC</sub> (usually written VCC)

- In NMOS and CMOS, written V<sub>DD</sub> (also VDD)

- Negative power supply (power sink)

- In TTL, written GND ("ground")

- In NMOS and CMOS, sometimes written V<sub>SS</sub> (also VSS)

- CMOS uses positive logic: VDD is logic "1", VSS is logic "0"

**CMOS Transistors as Switches**

Figure from Application-Specific Integrated Circuits, Smith, Addison-Wesley, 1997

Fall 2003, Lecture 29

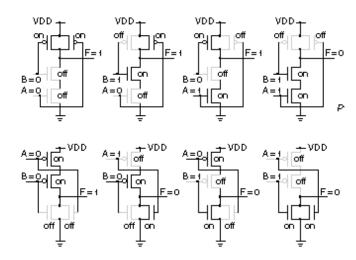

### CMOS NAND and NOR Gates

Figure from Application-Specific Integrated Circuits, Smith, Addison-Wesley, 1997

- Use two transistors to make a CMOS inverter (as shown on previous slide)

- Use four transistors to make a CMOS 2-input NAND gate

- Rule of thumb: 1 gate = 4 transistors

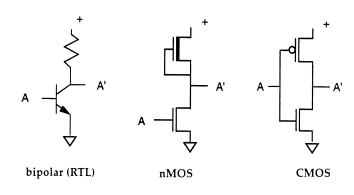

# IC Fabrication Technologies (Implementing an Inverter)

Figure from Modern VLSI Design, Wolf, Prentice Hall, 1994

- Bipolar transistor & resistor (fastest)

- NMOS n-channel depletion mode transistor (top) & n-channel enhancement mode transistor (bottom)

- CMOS p-channel (lowest power) enhancement mode transistor (top) & n-channel enhancement mode transistor (bottom)

Fall 2003, Lecture 29 4

Fall 2003, Lecture 29

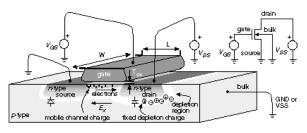

## **Cross-Section of an N-Channel Enhancement Mode MOS Transistor**

Figure from Application-Specific Integrated Circuits, Smith, Addison-Wesley, 1997

- Base is silicon *substrate* (*bulk*, *well*, *tub*) that's been *doped* with p-type impurities (full of positively-charged *holes*)

- Two diffusion areas heavily doped with ntype impurities (full of negatively-charged electrons) form the source and drain

- Transistor action takes place at the channel, connecting the source and drain

- A very thin layer of silicon dioxide (SiO<sub>2</sub>), called the *gate oxide*, insulates the *gate*, made of polysilicon, from the channel

Fall 2003, Lecture 29

# Operation of an N-Channel Enhancement Mode MOS Transistor (cont.)

- N-channel vs. p-channel

- N-channel: V<sub>GS</sub> and V<sub>DS</sub> both positive, gate and source are n-type (electrons), substrate & channel is p-type (holes), when V<sub>GS</sub> >> V<sub>t</sub> electrons accumulate in channel and flow from source to drain, current flows from drain to source

- P-channel: V<sub>GS</sub> and V<sub>DS</sub> both negative, gate and source are p-type (holes), substrate & channel is n-type (electrons), when V<sub>GS</sub> >> (more negative) than V<sub>t</sub> holes accumulate in channel and flow from source to drain, current flows from source to drain

- Current proportional to W/L of transistor

- Length (L) = parallel to current flow

- As W increases, more current can flow

Fall 2003, Lecture 29

As L increases, less current flows

### Operation of an N-Channel Enhancement Mode MOS Transistor

- Works as a switch gate-to-source voltage regulates the amount of current that can flow between drain and source

- When V<sub>GS</sub> = 0, the p-type channel is full of holes, and the n-type source and drain contain electrons

- The p-n junctions at source and drain form diodes in opposite directions, so no current flows between source and drain

- As V<sub>GS</sub> rises above 0, the few n-type impurities that are present in the p-type channel start to attract electrons

- The electrons migrate toward the (positively charged) gate, but are stopped by the gate oxide, so collect at the top of the channel

- When V<sub>GS</sub> rises to the threshold voltage (V<sub>t</sub>), enough electrons have collected to form an n-channel inversion layer, which allows electrons to flow from source to drain (current flows from drain to source)

Fall 2003, Lecture 29