# **Types of FPLDs**

light, which provides enough energy for

onto the bulk, returning the transistor to

Can be reprogrammed many times

normal operation

the electrons stuck on gate1 to jump back

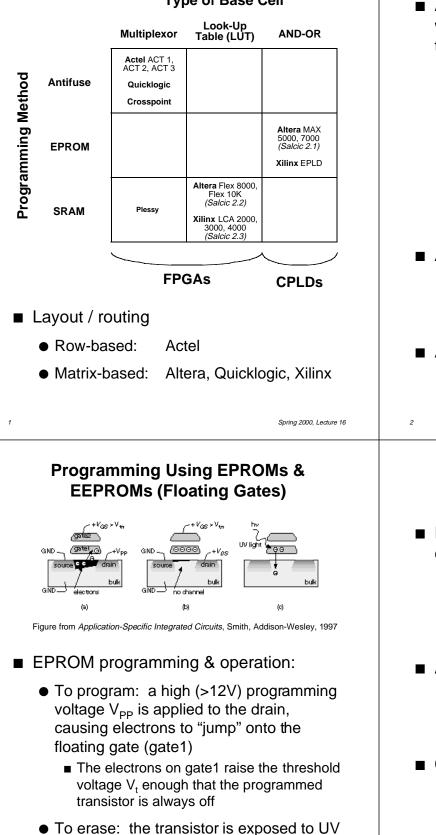

### Type of Base Cell

# **Programming Using Antifuses**

- An antifuse is normally open ("off"); when enough current (5–15mA) passes through it it closes ("on") • Current melts a thin insulating dielectric and forms a permanent silicon link • Disadvantage — can only program once Programmed in a special hardware device An antifuse FPLD may contain 750,000 antifuses, but only about 2% of them typically need to be programmed Takes about 5-10 minutes for each chip Advantages: Small — about the size of a via Low resistance, low capacitance = fast Antifuses can be used in FPLDs to : Connect inputs to cells Connect cells to interconnect Spring 2000, Lecture 16 **Programming Using EPROMS &** EEPROMs (Floating Gates) (cont.) EEPROMs are similar, but are erased electrically • Faster to erase than EPROM, and can be done "in-circuit" Requires larger cell than EEPROM Advantages • Can be programmed repeatedly, in-circuit Very small — requires only vertical space Can be used in FPLDs to : Connect inputs to cells NOR In NOR gate, when ~ OUT transistor is programmed IN1

- Connect cells to interconnect

(disabled), an input of 1

can not pull output down to VSS

3

Spring 2000, Lecture 16

IN2

INn

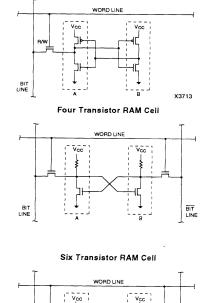

# Programming Using Static RAMs (SRAMs)

#### Five Transistor RAM Cell

Figure from Field-Programmable Gate Array Technology, Trimberger, Kluwer, 1994

#### Spring 2000, Lecture 16

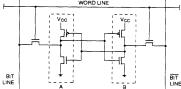

## Row-Based Layout

Figure from Application-Specific Integrated Circuits, Smith, Addison-Wesley, 1997

## Cells are arranged in rows

- Horizontal channels between rows

- Vertical channels above cells: some short, some long

- Each *channel* contains a fixed number of *tracks*, each track holds one wire

- Wires may be divided into fixed-length segments within each track

- In figure above, cell inputs connect to horizontal wires, outputs to vertical wires

## Programming Using Static RAMs (SRAMs) (cont.)

- Disadvantages:

- Must load configuration from ROM, disk, etc. on power-up

- Large requires several transistors

### Advantages:

- Can be programmed repeatedly, in-circuit

- Can be programmed quickly (< 1ms)</p>

- Part has been 100% tested at factory

- Same basic process as CMOS, so quickly takes advantage of new fab processes

- CMOS also requires less power than circuits requiring pull-up resistors

- SRAMs can be used in FPLDs to :

- Connect inputs to cells, or even to replace the cell if it's a LUT

- Connect cells to interconnect

Spring 2000, Lecture 16

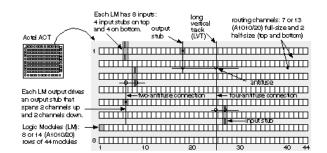

Figure from Application-Specific Integrated Circuits, Smith, Addison-Wesley, 1997

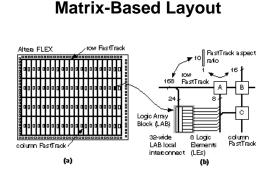

- Cells are arranged in an array (*matrix*)

- Horizontal and vertical channels between cells

- Each *channel* contains a fixed number of *tracks*, each track holds one wire

- In figure above:

- Cell inputs connect to horizontal tracks

- Box A connects cell output(s) to horizontal tracks, and box C connects cell output(s) to vertical tracks

- Box B acts as a switchbox between horizontal and vertical tracks

## **FPGA Pricing**

- Pricing = base price plus adjustments

- Discount for buying in quantity

- Discount for buying after process matures

- Premium for faster speed grade

- Premium for better package types

- Premium for industrial or military quality

- Some prices from distributors (2/26/98)

- Xilinx prices at http://www.marshall.com

- Biggest = 388 macrocells, fastest = 15ns (75 MHz), \$127 for 1–24, \$82 for >100

- Smallest = 36 macrocells, slowest = 15ns (75 MHz) \$5 for 1–24, \$3 for >100

- Fastest = 5ns (200 MHz), 36 macrocells \$19 for 1–24, \$12 for >100

9

Spring 2000, Lecture 16