- Very fast faster than general logic, since it's only a single level of logic

- Delay is predictable each RAM block is not scattered throughout the chip as in some FPGAs

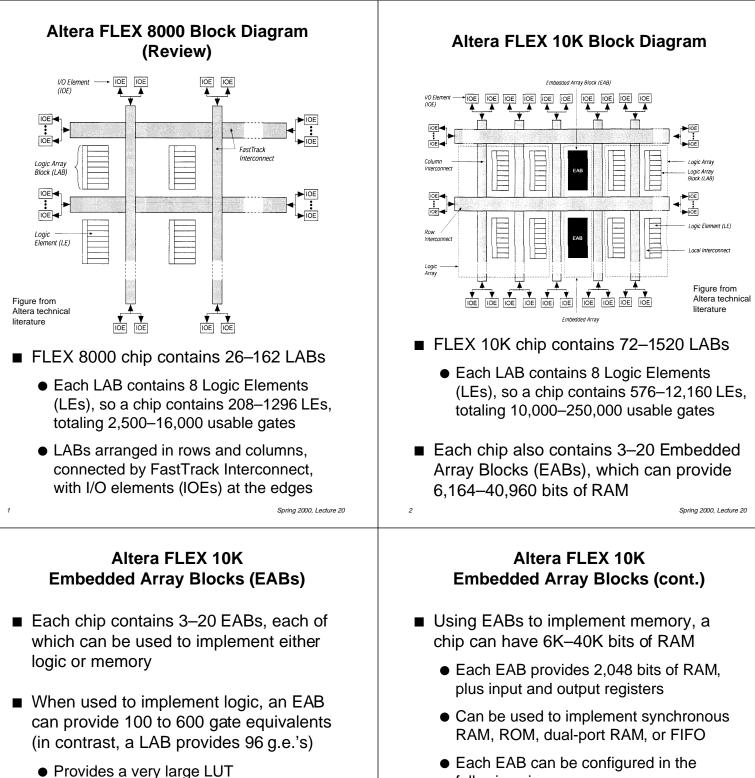

- Can be used to create complex logic functions such as multipliers (e.g., a 4x4 multiplier with 8 inputs and 8 outputs), microcontrollers, large state machines, and DSPs

- Each EAB can be used independently, or combined to implement larger functions

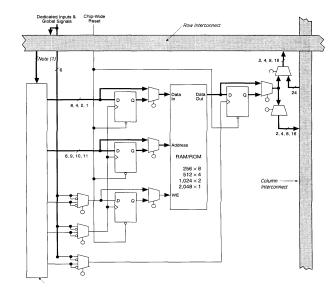

- following sizes:

- 256x8, 512x4, 1024x2, or 2048x1

- To get larger blocks, combine multiple EABs:

- Example: combine two 256x8 RAM blocks to form a 256x16 RAM block

- Example: combine two 512x4 RAM blocks to form a 512x8 RAM block

- Can even combine all EABs on the chip into one big RAM block

- Can combine so as to form blocks up to 2048 words without impacting timing

## Altera FLEX 10K Embedded Array Blocks (cont.)

Figure from Altera technical literature

- EAB gets input from a row channel, and can output to up to 2 row channels and 2 column channels

- Input and output buffers are available

## **APEX LABs and Interconnect**

- Logic Array Block (LAB)

- 10 LEs

5

- Interleaved local interconnect (each LE connects to 2 local interconnect, each local interconnect connects to 10 LEs)

- Each LE can connect to 29 other Les through local interconnect

- Logic Element (LE)

- 4-input LUT, carry chain, cascade chain, same as FLEX devices

- Synchronous and asynchronous load and clear logic

- Interconnect

- MegaLAB interconnect between 16 LABs, etc. inside each MegaLAB

- FastTrack row and column interconnect between MegaLABs

## Altera APEX 20K Overview

- APEX 20K chip contains:

- 256–3,456 LABs, each of which contains 10 Logic Elements (LEs), so a chip contains 2,560–51,840 Les, 162,000–2,391,552 usable gates

- 16–216 Embedded System Blocks (EABs), each of which can provide 32,768–442,368 bits of memory

- Can implement CAM, RAM, dual-port RAM, ROM, and FIFO

- Organization:

- MultiCore architecture, combining LUT, product-terms, & memory in one structure

- Designed for "system on a chip"

- MegaLAB structures, each of which contains 16 LABs, one ESB, and a MegaLAB interconnect (for routing within the MegaLAB)

- ESB provides product terms <u>or</u> memory

Spring 2000, Lecture 20

## APEX Embedded System Blocks (ESBs)

- Each ESB can act as a macrocell and provide product terms

- Each ESB gets 32 inputs from local interconnect, from adjacent LAB or MegaLAB interconnect

- In this mode, each ESB contains 16 macrocells, and each macrocell contains 2 product terms and a programmable register (parallel expanders also provided)

- Each ESB can also act as a memory block (dual-port RAM, ROM, FIFO, or CAM memory) configured in various sizes

- Inputs from adjacent local interconnect, which can be driven from MegaLAB or FastTrack interconnect

- Outputs to MegaLAB and FastTrack, some outputs to local interconnect

Spring 2000, Lecture 20